# INT5500 Intellon Turbo Powerline IC

#### **Features**

- Single-chip powerline networking transceiver with integrated MII interface

- Up to 85 Mbps data rate on the powerline

- Direct connection to Intellon INT1200 Analog Front End IC

- HomePlug 1.0 compatible

- Supports QAM 256/64/16, DQPSK, DBPSK and ROBO modulation schemes

- Multi-vendor flash compatibility

- Low power consumption

- Orthogonal Frequency Division Multiplexing (OFDM) with patented signal processing techniques for high data reliability in noisy media conditions

- Intelligent channel adaptation maximizes throughput under harsh channel conditions

- Integrated Quality of Service (QoS) features such as prioritized random access, contention-free access, and segment bursting

- 56-bit DES Link Encryption with key management for secure powerline communications

- In-circuit initialization of Flash memory via host interface

- "Boot From Host" and "Field-Upgradeable Firmware" features

- 1.8V core, 3.3V I/O Signaling

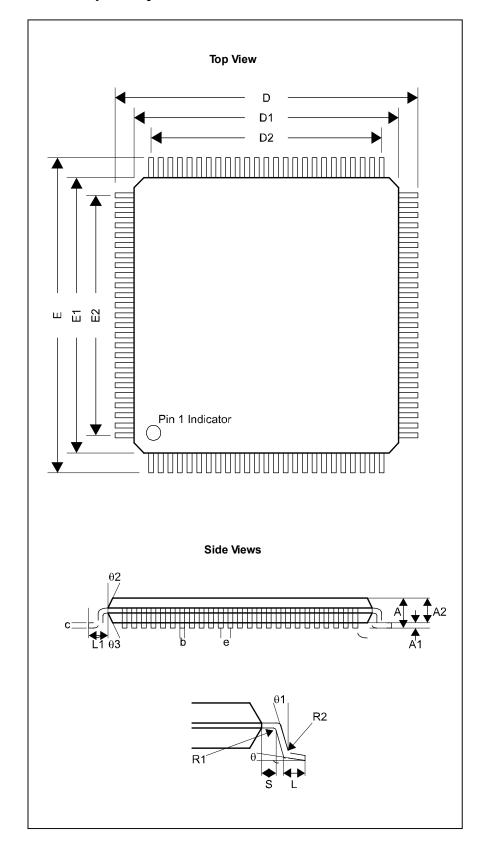

- 100-pin LQFP small footprint package

# **Applications**

- Standard Video TV (SDTV) Distribution

- TV over IP (IPTV)

- Higher data rate broadband sharing

- Shared broadband internet access

- Audio and video streaming and transfer

- Expanding the coverage of wireless LANs

- Voice Over IP calls

- PC file and application sharing

- Printer and peripheral sharing

- Network and online gaming

- Security cameras

# **CONTENTS**

| 1.          | General Description                      | 3    |

|-------------|------------------------------------------|------|

| 2.          | Block Diagram                            |      |

| 3.          | Master Pin Diagram                       |      |

| <b>1.</b>   | Master Pin I/O                           |      |

| 5.          | Pin Description                          | 7    |

| <b>6.</b>   | INT5500 System Overview                  | . 10 |

| 6.1.        | MII Host/DTE Mode                        | . 10 |

| 6.2.        | MII PHY Mode                             | . 11 |

| 6.3.        | Pin Assignment in Different INT5500 Mode | . 12 |

| 7.          | Design Considerations                    |      |

| 7.1.        | MAC Firmware Boot Option                 | . 17 |

| 7.2.        |                                          |      |

| 7.3.        |                                          |      |

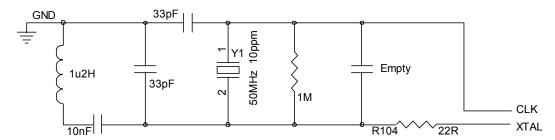

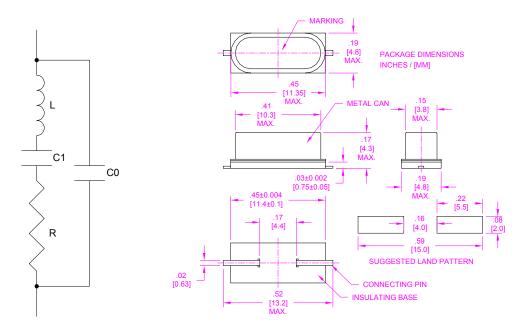

| 7.4.        | Crystal Oscillator Circuit               | . 20 |

| 7.5.        | ·                                        |      |

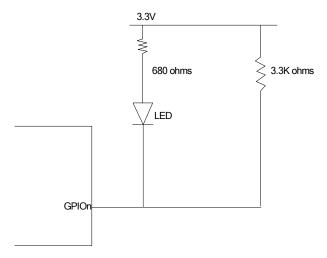

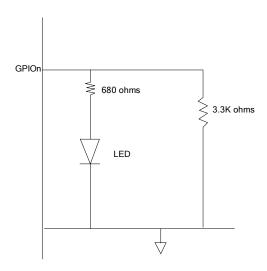

| <b>7.6.</b> | LED Function/GPIO Strapping              | . 21 |

| 7.7.        | ** 9                                     |      |

| 8.          | User Protocol Interface                  |      |

| 8.1.        | HomePlug MAC Management                  | . 23 |

| 9.          | Specifications                           | . 38 |

| 9.1.        | Electrical Specifications                | . 38 |

| 9.2.        | Crystal Specifications                   | . 39 |

| 9.3.        | Physical Specifications                  | . 40 |

| 10.         | Switching Characteristics                | . 41 |

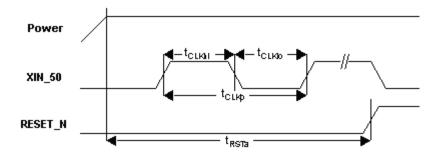

| 10.1        | 1. System Clock and Reset Timing         | . 41 |

| 10.2        | 2. Analog Front End Interface Timing     | . 42 |

| 10.3        |                                          |      |

| 10.4        | 6                                        |      |

| 11.         | Revision History                         | . 47 |

# 1. General Description

The INT5500 IC is an integrated powerline MAC/PHY providing *No New Wires* communications to any room, over any wire, at speeds of up to 85 Mbps. The INT5500 alternately provides two interfaces, via pin-out options:

- INT5500 (PHY Option): An MII PHY (IEEE 802.3u 1995, Paragraph 22) interface for interconnection to microcontrollers or Ethernet controllers. The INT5500 (PHY Option) is selected by strapping ASC\_DATA/ Mode pin (pin 3) to VDD\_IO through a 3.3KΩ resistor.

- INT5500 (Host/DTE Option): An MII Host/DTE interface (IEEE 802.3u 1995, Paragraph 22) for interconnection to an Ethernet PHY. The INT5500 (Host/DTE Option) is selected by connecting ASC DATA/ Mode pin (pin 3) to VSS (GND) through a 3.3KΩ resistor.

The INT5500 Turbo powerline IC implements Intellon's patented technology and is fully compatible with the *HomePlug 1.0 Specification*. Specifically tailored to reliably deliver up to 85 Mbps over the difficult powerline communication environment, the IC combats deep attenuation notches, noises sources, and multi-path fading by allocating usable frequencies according to the signal to noise ratio (SNR). Synchronization is achieved in low SNR channels without the use of pilot carriers. Inclusion of additional modulation schemes (QAM 256/64/16) increases the chipset's capability to attain higher throughput performance. The MAC implements a CSMA/CA scheme with prioritization and automatic repeat request (ARQ) for reliable delivery of Ethernet packets via packet encapsulation.

Built-in Quality of Service (QoS) features provide the necessary bandwidth for multimedia payloads including voice, data, audio, and video. A four-level prioritized random access method exists with strict adherence to priority. Segment bursting on the powerline minimizes the demands on the receiver resources and maximizes the throughput of the network while still providing excellent latency response and jitter performance. The IC's contention-free access capability extends this concept of segment bursting to allow the transmission of multiple frames over the powerline without relinquishing the control of the medium.

The INT5500 operates on 1.8V core and 3.3V I/O power, and is packaged in a 100-pin LQFP. Intellon offers a complete solution for powerline communication applications by providing the INT5500 in conjunction with the INT1200 Analog Front End IC.

Intellon Confidential 3 24002694 Rev. 2

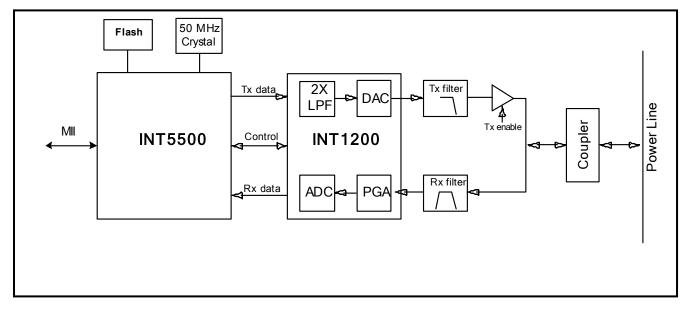

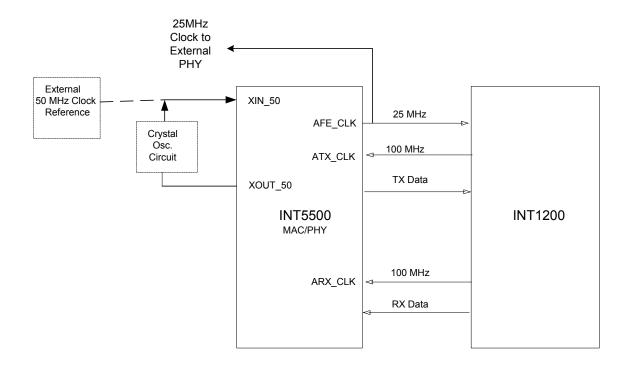

Figure 1: A General System Block Diagram of an INT5500CS based Powerline Device

# 2. Block Diagram

Figure 2: INT5500 IC Block Diagram

# 3. Master Pin Diagram

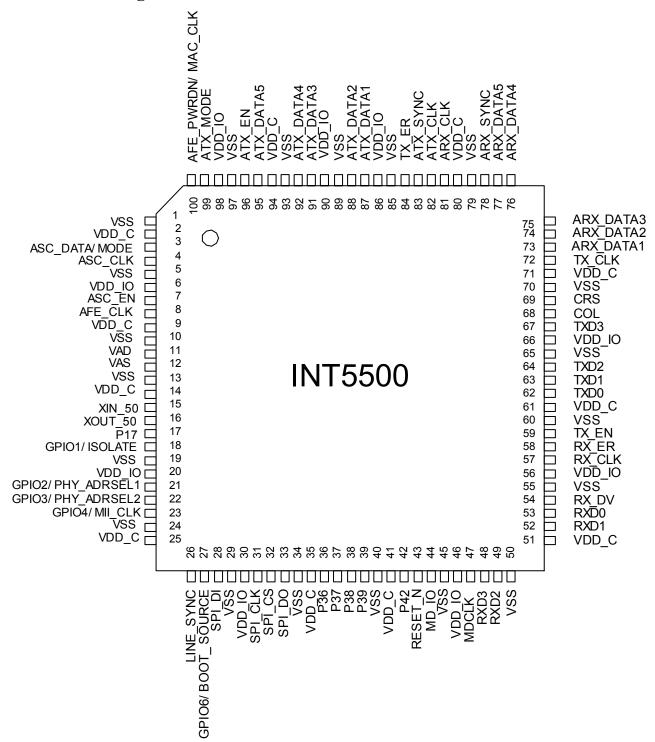

Figure 3: INT5500 IC Master Pin Diagram

# 4. Master Pin I/O

| Pin No. | Signal             | Pin No. | Signal             |

|---------|--------------------|---------|--------------------|

| 1       | VSS                | 51      | VDD_C              |

| 2       | VDD_C              | 52      | RXD1               |

| 3       | ASC_DATA/ MODE     | 53      | RXD0               |

| 4       | ASC_CLK            | 54      | RX_DV              |

| 5       | VSS                | 55      | VSS                |

| 6       | VDD_IO             | 56      | VDD_IO             |

| 7       | ASC EN             | 57      | RX CLK             |

| 8       | AFE_CLK            | 58      | RX_ER              |

| 9       | VDD_C              | 59      | TX_EN              |

| 10      | VSS                | 60      | VSS                |

| 11      | VAD                | 61      | VDD C              |

| 12      | VAS                | 62      | TXD0               |

| 13      | VSS                | 63      | TXD1               |

| 14      | VDD_C              | 64      | TXD2               |

| 15      | XIN_50             | 65      | VSS                |

| 16      | XOUT 50            | 66      | VDD IO             |

| 17      | P17                | 67      | TXD3               |

| 18      | GPIO1/ ISOLATE     | 68      | COL                |

| 19      | VSS                | 69      | CRS                |

| 20      | VDD IO             | 70      | VSS                |

| 21      | GPIO2/ PHY ADRSEL1 | 71      | VDD C              |

| 22      | GPIO3/ PHY ADRSEL2 | 72      | TX CLK             |

| 23      | GPIO4/ MII CLK     | 73      | ARX DATA1          |

| 24      | VSS                | 74      | ARX DATA2          |

| 25      | VDD C              | 75      | ARX DATA3          |

| 26      | LINE SYNC          | 76      | ARX DATA4          |

| 27      | GPIO6/ BOOT SOURCE | 77      | ARX DATA5          |

| 28      | SPI DI             | 78      | ARX SYNC           |

| 29      | VSS                | 79      | VSS                |

| 30      | VDD IO             | 80      | VDD C              |

| 31      | SPI CLK            | 81      | ARX CLK            |

| 32      | SPI CS             | 82      | ATX CLK            |

| 33      | SPI DO             | 83      | ATX SYNC           |

| 34      | VSS                | 84      | TX ER              |

| 35      | VDD C              | 85      | VSS                |

| 36      | P36                | 86      | VDD IO             |

| 37      | P37                | 87      | ATX DATA1          |

| 38      | P38                | 88      | ATX DATA2          |

| 39      | P39                | 89      | VSS                |

| 40      | VSS                | 90      | VDD IO             |

| 41      | VDD C              | 91      | ATX DATA3          |

| 42      | P42                | 92      | ATX DATA4          |

| 42      | RESET N            | 93      | VSS                |

| 43      | MD IO              | 93      | VDD C              |

| 45      | VSS                | 95      | ATX DATA5          |

| 46      | VDD IO             | 96      | ATX EN             |

| 47      | MDCLK              | 97      | VSS VSS            |

| 48      | RXD3               | 98      | VDD IO             |

| 48      | RXD2               | 98      | ATX MODE           |

|         |                    | _       |                    |

| 50      | VSS                | 100     | AFE_PWRDN/ MAC_CLK |

# 5. Pin Description

| Pin No. | Signal              | Description                                                                       |  |

|---------|---------------------|-----------------------------------------------------------------------------------|--|

| 1       | VSS                 | Ground                                                                            |  |

| 2       | VDD_C               | 1.8V Core Supply Voltage                                                          |  |

| 3       | ASC_DATA/ MODE      | AFE Serial Interface Data                                                         |  |

|         |                     | The pull-up/ pull-down value is latched as MODE input during                      |  |

|         |                     | power up/ reset. Refer section 7.2 for more details.                              |  |

| 4       | ASC_CLK             | AFE serial interface clock.                                                       |  |

|         |                     |                                                                                   |  |

|         | 7700                | This pin must be pulled low at power-up/reset.                                    |  |

| 5       | VSS                 | Ground                                                                            |  |

| 6       | VDD_IO              | 3.3V I/O Supply Voltage                                                           |  |

| 7       | ASC_EN              | Active low AFE serial interface strobe.                                           |  |

|         |                     | This pin to be pulled law during power up/reset                                   |  |

| 8       | AFE CLK             | This pin to be pulled low during power up/ reset.  25 MHz clock reference to AFE. |  |

| 9       | VDD C               | 1.8V Core Supply Voltage                                                          |  |

| 10      | VSS VSS             | Ground                                                                            |  |

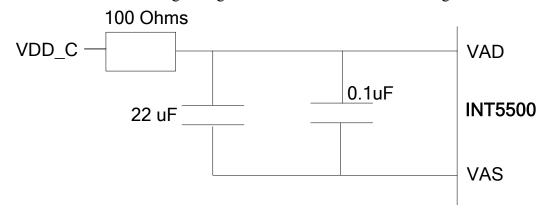

| 11      | VAD                 | PLL VDD (1.8 V). Refer to section 7.5 for more details.                           |  |

| 12      | VAS                 | PLL VSS (ground). Refer to section 7.5 for more details.                          |  |

| 13      | VSS                 | Ground                                                                            |  |

| 14      | VDD C               | 1.8V Core Supply Voltage                                                          |  |

| 15      | XIN 50              | 50 MHz clock logic signal input or crystal connection.                            |  |

| 16      | XOUT 50             | 50 MHz clock crystal connection (when using built-in                              |  |

| 10      | A001_30             | oscillator).                                                                      |  |

| 17      | P17                 | Connect to VSS through a 3.3KΩ resistor                                           |  |

| 18      | GPIO1/ ISOLATE      | General-Purpose Input/Output 1.                                                   |  |

| 10      | GIIOI, ISOLITIE     | General Larpose input output 1.                                                   |  |

|         |                     | The pull-up/ pull-down value is latched as MII ISOLATE input                      |  |

|         |                     | INT5500 PHY mode during power up/ reset. Refer section 7.2                        |  |

|         |                     | for more details.                                                                 |  |

| 19      | VSS                 | Ground                                                                            |  |

| 20      | VDD_IO              | 3.3V I/O Supply Voltage                                                           |  |

| 21      | GPIO2/ PHY_ADRSEL1  | General-Purpose Input/Output 2.                                                   |  |

|         |                     |                                                                                   |  |

|         |                     | The pull-up/ pull-down value is latched as PHY Address Select                     |  |

|         |                     | input during power up/reset in the INT5500 PHY mode. Refer                        |  |

| 22      | GPIO3/ PHY ADRSEL2  | section 7.2 for more details.  General-Purpose Input/Output 3.                    |  |

| 22      | GF103/ FH1_ADRSEL2  | General-Purpose Input/Output 5.                                                   |  |

|         |                     | The pull-up/ pull-down value is latched as PHY Address Select                     |  |

|         |                     | input during power up/ reset in the INT5500 PHY mode. Refer                       |  |

|         |                     | section 7.2 for more details.                                                     |  |

| 23      | GPIO4/ MII CLK      | General-Purpose Input/Output 4.                                                   |  |

|         | _                   |                                                                                   |  |

|         |                     | The pull-up/ pull-down value is latched to select MII clock                       |  |

|         |                     | speed in INT5500 PHY mode during power up/ reset. Refer                           |  |

|         |                     | section 7.2 for more details.                                                     |  |

| 24      | VSS                 | Ground                                                                            |  |

| 25      | VDD_C               | 1.8V Core Supply Voltage                                                          |  |

| 26      | LINE_SYNC           | Line Sync                                                                         |  |

| 27      | GPIO6/ BOOT_ SOURCE | General-Purpose Input/Output 6.                                                   |  |

|         |                     | The pull-up/ pull-down value is latched as Boot Source input                      |  |

|         |                     | during power up/ reset. Refer section 7.2 for more details.                       |  |

| 28      | SPI_DI              | Non-Volatile Memory SPI interface data input.                                     |  |

|         | _                   |                                                                                   |  |

| 29      | VSS                 | Ground                                                                            |  |

| 30      | VDD_IO              | 3.3V I/O Supply Voltage                                                           |  |

| 31      | SPI_CLK             | Non-Volatile Memory SPI interface clock.                                          |  |

| Pin No. | Signal    | Description                                                                                                                                                                                                                                                                                                          |  |

|---------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 32      | SPI_CS    | Non-Volatile Memory SPI interface chips select (active low).                                                                                                                                                                                                                                                         |  |

| 33      | SPI_DO    | Non-Volatile Memory SPI interface data out.                                                                                                                                                                                                                                                                          |  |

| 34      | VSS       | Ground                                                                                                                                                                                                                                                                                                               |  |

| 35      | VDD_C     | 1.8V Core Supply Voltage                                                                                                                                                                                                                                                                                             |  |

| 36      | P36       | Connect to VDD_IO through a 3.3KΩ resistor.                                                                                                                                                                                                                                                                          |  |

| 37      | P37       | Connect to VSS through a 3.3KΩ resistor                                                                                                                                                                                                                                                                              |  |

| 38      | P38       | Connect to VDD_IO through a 3.3KΩ resistor                                                                                                                                                                                                                                                                           |  |

| 39      | P39       | Connect to VDD IO through a 3.3KΩ resistor                                                                                                                                                                                                                                                                           |  |

| 40      | VSS       | Ground                                                                                                                                                                                                                                                                                                               |  |

| 41      | VDD_C     | 1.8V Core Supply Voltage                                                                                                                                                                                                                                                                                             |  |

| 42      | P42       | Connect to VDD IO through a 3.3KΩ resistor                                                                                                                                                                                                                                                                           |  |

| 43      | RESET N   | Reset Input. Resets all IC logic when low.                                                                                                                                                                                                                                                                           |  |

| 44      | MD IO     | MII Management Data Input/Output                                                                                                                                                                                                                                                                                     |  |

| 45      | VSS       | Ground                                                                                                                                                                                                                                                                                                               |  |

| 46      | VDD_IO    | 3.3V I/O Supply Voltage                                                                                                                                                                                                                                                                                              |  |

| 47      | MDCLK     | MII Management Data Clock                                                                                                                                                                                                                                                                                            |  |

| 48      | RXD3      | MII RX Data bit 3                                                                                                                                                                                                                                                                                                    |  |

| 49      | RXD2      | MII RX Data bit 2                                                                                                                                                                                                                                                                                                    |  |

| 50      | VSS       | Ground                                                                                                                                                                                                                                                                                                               |  |

| 51      | VDD_C     | 1.8V Core Supply Voltage                                                                                                                                                                                                                                                                                             |  |

| 52      | RXD1      | MII RX Data bit 1                                                                                                                                                                                                                                                                                                    |  |

| 53      | RXD0      | MII RX Data bit 0                                                                                                                                                                                                                                                                                                    |  |

| 54      | RX_DV     | MII RX Data Valid                                                                                                                                                                                                                                                                                                    |  |

| 55      | VSS       | Ground                                                                                                                                                                                                                                                                                                               |  |

| 56      | VDD_IO    | 3.3V I/O Supply Voltage                                                                                                                                                                                                                                                                                              |  |

| 57      | RX_CLK    | MII RX Clock                                                                                                                                                                                                                                                                                                         |  |

| 58      | RX_ER     | MII RX Error                                                                                                                                                                                                                                                                                                         |  |

| 59      | TX_EN     | MII TX Enable                                                                                                                                                                                                                                                                                                        |  |

| 60      | VSS       | Ground                                                                                                                                                                                                                                                                                                               |  |

| 61      | VDD_C     | 1.8V Core Supply Voltage                                                                                                                                                                                                                                                                                             |  |

| 62      | TXD0      | MII TX data bit 0                                                                                                                                                                                                                                                                                                    |  |

| 63      | TXD1      | MII TX data bit 1                                                                                                                                                                                                                                                                                                    |  |

| 64      | TXD2      | MII TX data bit 2                                                                                                                                                                                                                                                                                                    |  |

| 65      | VSS       | Ground                                                                                                                                                                                                                                                                                                               |  |

| 66      | VDD_IO    | 3.3V I/O Supply Voltage                                                                                                                                                                                                                                                                                              |  |

| 67      | TXD3      | MII TX data bit 3                                                                                                                                                                                                                                                                                                    |  |

| 68      | COL       | MII Collision Detect                                                                                                                                                                                                                                                                                                 |  |

| 69      | CRS       | MII Carrier Sense                                                                                                                                                                                                                                                                                                    |  |

| 70      | VSS       | Ground                                                                                                                                                                                                                                                                                                               |  |

| 71      | VDD_C     | 1.8V Core Supply Voltage                                                                                                                                                                                                                                                                                             |  |

| 72      | TX_CLK    | MII TX Clock                                                                                                                                                                                                                                                                                                         |  |

| 73      | ARX_DATA1 | AFE receive data.                                                                                                                                                                                                                                                                                                    |  |

| 74      | ARX_DATA2 | Data is received from the AFE on this bus synchronous to                                                                                                                                                                                                                                                             |  |

| 75      | ARX_DATA3 | ARX_CLK with upper/lower nibble framed by ARX_SYNC. This is a time division-multiplexed data bus that carries 10-bit                                                                                                                                                                                                 |  |

| 76      | ARX_DATA4 | received data in two nibbles of 5 bits each. The receive data rate                                                                                                                                                                                                                                                   |  |

| 77      | ARX_DATA5 | is 50 MSPS giving a nibble rate of 100 MHz                                                                                                                                                                                                                                                                           |  |

| 78      | ARX_SYNC  | AFE receive data synchronization strobe.  Low: indicates that the MS nibble of the data is present on ARX_DATA [].  High: indicates that the LS nibble of the data is present on ARX_DATA [].  For every word that passes across the interface, the MS nibble always appears first followed by the LS nibble second. |  |

| 79      | VSS       | Ground                                                                                                                                                                                                                                                                                                               |  |

| 80      | VDD C     | 1.8V Core Supply Voltage                                                                                                                                                                                                                                                                                             |  |

| 81      | ARX_CLK   | AFE receive data clock (100 MHz).                                                                                                                                                                                                                                                                                    |  |

|         | _         | Note that this pin is not 5 V-tolerant                                                                                                                                                                                                                                                                               |  |

| D: N     | G: 1               | D 1.1                                                              |  |

|----------|--------------------|--------------------------------------------------------------------|--|

| Pin No.  | Signal             | Description                                                        |  |

| 82       | ATX_CLK            | AFE transmit data clock (100 MHz).                                 |  |

|          |                    | Note that this pin is not 5 V-tolerant                             |  |

| 83       | ATX_SYNC           | AFE transmit data synchronization strobe.                          |  |

|          |                    | Low: indicates that the MS nibble is present on the                |  |

|          |                    | ATX_DATA [] bus.                                                   |  |

|          |                    | High: indicates that the LS nibble is present on                   |  |

|          |                    | the ATX_DATA [] bus.                                               |  |

|          |                    | For every word that passes across the interface, the MS nibble     |  |

|          |                    | always appears first followed by the LS nibble second.             |  |

|          |                    | Note: ATX_SYNC remains low while ATX_MODE is asserted              |  |

| 0.4      | TOTAL EDD          | as gain data is not multiplexed                                    |  |

| 84       | TX_ER              | MII transmit data error.                                           |  |

| 85<br>86 | VSS<br>VDD IO      | Ground                                                             |  |

| 87       | ATX DATA1          | 3.3V I/O Supply Voltage AFE transmit data bus.                     |  |

| 88       | ATX DATA2          | AFE transmit data bus.                                             |  |

| 91       | ATX DATA3          | This is a time division-multiplexed data bus that carries 10-bit   |  |

| 92       | ATX DATA4          | transmit data in two nibbles of 5 bits each. The transmit rate is  |  |

| 95       | ATX DATA5          | 50 MSPS giving a nibble rate of 100 MHz. While ATX_MOD             |  |

| 73       | AIA_DAIAS          | is asserted, this bus carries 5-bit non-multiplexed gain data for  |  |

|          |                    | the receive path.                                                  |  |

| 89       | VSS                | Ground                                                             |  |

| 90       | VDD_IO             | 3.3V I/O Supply Voltage                                            |  |

| 93       | VSS                | Ground                                                             |  |

| 94       | VDD_C              | 1.8V Core Supply Voltage                                           |  |

| 96       | ATX_EN             | Transmit enable.                                                   |  |

|          |                    | Asserted: indicates that a transmission is in progress.            |  |

|          |                    | Negated: indicates that a transmission is not in progress (receive |  |

|          |                    | mode).                                                             |  |

| 97       | VSS                | Ground                                                             |  |

| 98       | VDD IO             | 3.3V I/O Supply Voltage                                            |  |

| 99       | ATX_MODE           | AFE gain transmit data port mode.                                  |  |

| 100      | AFE_PWRDN/ MAC_CLK | AFE power down.                                                    |  |

|          |                    | The pull-up/ pull-down value is latched to select MAC Clock        |  |

|          |                    | speed during power up/ reset. Refer section 7.2 for more           |  |

|          |                    | details.                                                           |  |

| L        | l .                |                                                                    |  |

Intellon Confidential 9 24002694 Rev. 2

# 6. INT5500 System Overview

The INT5500 is set up in one of the two configurations: Host/DTE Mode and PHY Mode.

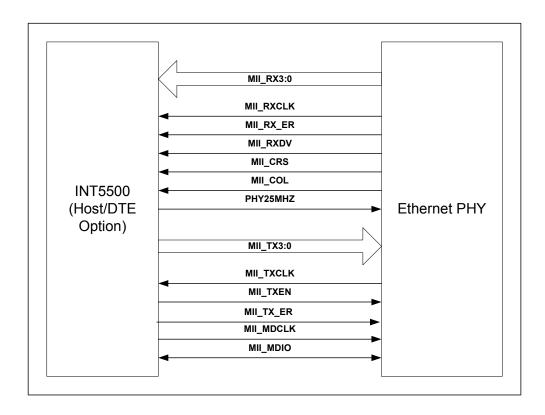

#### 6.1. MII Host/DTE Mode

The INT5500 implements an MII interface as defined by the IEEE 802.3u. This interface comprises a data interface and a management interface. The data interface is used for exchanging data between the INT5500 and the 802.3u compliant MII PHY. The management interface allows the INT5500 to control and monitor the attached Ethernet PHY.

The MII data interface consists of separate 4-bit data paths for transmit and receive data along with carrier sense and collision detection. Data is transferred between the MAC and PHY over each 4-bit data path synchronous with a clock signal supplied to the INT5500 (Host/DTE Option) by the Ethernet PHY.

The MII management interface provides access to the status and control registers in the Ethernet PHY. Further details of the MII can be found in the IEEE 802.3u Standard.

The MAC firmware image is loaded from an external serial flash. The serial flash is used to store MAC configuration information and MAC Non-Volatile Parameters (e.g. NEK).

Figure 4: MII Interface to INT5500 (Host/DTE Option)

Intellon Confidential 10 24002694 Rev. 2

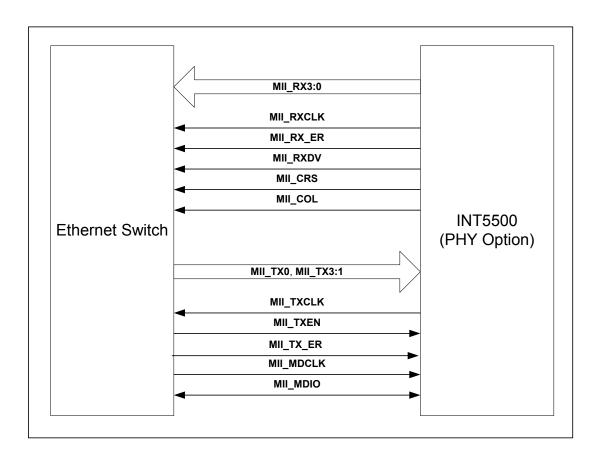

#### 6.2. MII PHY Mode

MII is an industry standard, multi vendor, interoperable interface between the MAC and PHY sub-layers. It provides a simple interconnection between the INT5500 and IEEE 802.3u Ethernet MAC controllers from a variety of sources. The MII consists of separate 4-bit data paths for transmit and receive data along with carrier sense and collision detection. Data is transferred between the MAC and PHY over each 4-bit data path synchronous with a clock signal supplied to the MAC by the INT5500. The MII interface also provides a two-wire bi-directional serial management data interface. This interface provides access to the status and control registers in the INT5500. Further details of the MII can be found in the IEEE 802.3u Standard.

The MAC firmware shall be downloaded to the INT5500 over the host interface (MII) at system initialization or from the serial flash.

Figure 5: MII Interface to INT5500 (PHY Option)

Intellon Confidential 11 24002694 Rev. 2

# 6.3. Pin Assignment in Different INT5500 Mode

|            |                       | PHY Mode (I/O)                                                                                                                                                                                           | Host/ DTE Mode (I/O)                                                                                                                                                                                       |

|------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin<br>No. | Signal                | PHY mode is selected by connecting the ASC_DATA/MODE (pin3) to VDD_IO through a 3.3KΩ resistor                                                                                                           | Host/DTE mode is selected by connecting the ASC_DATA/MODE (pin3) to VSS through a 3.3KΩ resistor                                                                                                           |

| 1          | VSS                   | Ground (I)                                                                                                                                                                                               | Ground (I)                                                                                                                                                                                                 |

| 2          | VDD C                 | 1.8V Core Supply Voltage (I)                                                                                                                                                                             | 1.8V Core Supply Voltage (I)                                                                                                                                                                               |

| 3          | ASC_DATA/<br>MODE     | AFE Serial Interface Data. (I/O) The pull-up/ pull-down value is latched as MODE during power up/ reset. PHY mode is selected by connecting the ASC_DATA/ MODE (pin3) to VDD_IO through a 3.3KΩ resistor | AFE Serial Interface Data (I/O) The pull-up/ pull-down value is latched as MODE during power up/ reset. Host/ DTE mode is selected by connecting the ASC_DATA/ MODE (pin3) to VSS through a 3.3KΩ resistor |

| 4          | ASC_CLK               | AFE serial interface clock. (O) This pin must be pulled low.                                                                                                                                             | AFE serial interface clock (O) This pin must be pulled low.                                                                                                                                                |

| 5          | VSS                   | Ground (I)                                                                                                                                                                                               | Ground (I)                                                                                                                                                                                                 |

| 6          | VDD_IO                | 3.3V I/O Supply Voltage (I)                                                                                                                                                                              | 3.3V I/O Supply Voltage (I)                                                                                                                                                                                |

| 7          | ASC_EN                | Active low AFE serial interface strobe (O).                                                                                                                                                              | Active low AFE serial interface strobe (O).                                                                                                                                                                |

| 8          | AFE_CLK               | 25 MHz clock reference to AFE (O).                                                                                                                                                                       | 25 MHz clock reference to AFE (O).                                                                                                                                                                         |

| 9          | VDD_C                 | 1.8V Core Supply Voltage (I)                                                                                                                                                                             | 1.8V Core Supply Voltage (I)                                                                                                                                                                               |

| 10         | VSS                   | Ground (I)                                                                                                                                                                                               | Ground (I)                                                                                                                                                                                                 |

| 11         | VAD                   | PLL VDD (1.8 V). Refer to section 7.5 for more details                                                                                                                                                   | PLL VDD (1.8 V). Refer to section 7.5 for more details                                                                                                                                                     |

| 12         | VAS                   | PLL VSS (ground). Refer to section 7.5 for more details                                                                                                                                                  | PLL VSS (ground). Refer to section 7.5 for more details                                                                                                                                                    |

| 13         | VSS                   | Ground (I)                                                                                                                                                                                               | Ground (I)                                                                                                                                                                                                 |

| 14         | VDD_C                 | 1.8V Core Supply Voltage (I)                                                                                                                                                                             | 1.8V Core Supply Voltage (I)                                                                                                                                                                               |

| 15         | XIN_50                | 50 MHz clock logic signal input or crystal connection (I).                                                                                                                                               | 50 MHz clock logic signal input or crystal connection (I).                                                                                                                                                 |

| 16         | XOUT_50               | 50 MHz clock crystal connection (when using built-in oscillator) (O).                                                                                                                                    | 50 MHz clock crystal connection (O)                                                                                                                                                                        |

| 17         | P17                   | Connect to VSS through a 3.3KΩ resistor                                                                                                                                                                  | Connect to VSS through a 3.3KΩ resistor                                                                                                                                                                    |

| 18         | GPIO1/<br>ISOLATE     | General-Purpose Input/Output 1 (I/O) The pull-up/ pull-down value is latched as MII ISOLATE input during power up/ reset. Refer section 7.2 for more details.                                            | General-Purpose Input/Output 1 (I/O). This pin shall be tied LOW during power up/reset.                                                                                                                    |

| 19         | VSS                   | Ground (I)                                                                                                                                                                                               | Ground (I)                                                                                                                                                                                                 |

| 20         | VDD_IO                | 3.3V I/O Supply Voltage (I)                                                                                                                                                                              | 3.3V I/O Supply Voltage (I)                                                                                                                                                                                |

| 21         | GPIO2/<br>PHY_ADRSEL1 | General-Purpose Input/Output 2 (I/O). The pull-up/ pull-down value is latched as PHY Address Select input during power up/ reset in the INT5500 PHY mode. Refer section 7.2 for more details             | General-Purpose Input/Output 2 (I/O). This pin shall be tied HIGH during power up/reset.                                                                                                                   |

| 22         | GPIO3/<br>PHY_ADRSEL2 | General-Purpose Input/Output 3 (I/O). The pull-up/ pull-down value is latched as PHY Address Select input during power up/ reset in the INT5500 PHY mode. Refer section 7.2 for more details             | General-Purpose Input/Output 3 (I/O). This pin shall be tied LOW during power up/reset.                                                                                                                    |

| 23         | GPIO4/<br>MII_CLK     | General-Purpose Input/Output 4 (I/O) The pull-up/ pull-down value is latched to select MII clock speed in INT5500 PHY mode during power up/ reset. Refer section 7.2 for more details                    | General-Purpose Input/Output 4 (I/O). This pin should be tied HIGH during power up/ reset.                                                                                                                 |

|       |                                       | PHY Mode (I/O)                                                                   | Host/ DTE Mode (I/O)                                                             |

|-------|---------------------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| Pin   | Cianal                                | · · ·                                                                            | ` ′                                                                              |

| No.   | Signal                                | PHY mode is selected by connecting the                                           | Host/DTE mode is selected by connecting                                          |

| 110.  |                                       | ASC_DATA/ MODE (pin3) to VDD_IO through a 3.3K $\Omega$ resistor                 | the ASC_DATA/MODE (pin3) to VSS through a 3.3KΩ resistor                         |

|       |                                       | -                                                                                | <u> </u>                                                                         |

| 24    | VSS                                   | Ground                                                                           | Ground                                                                           |

| 25    | VDD_C                                 | 1.8V Core Supply Voltage (I)                                                     | 1.8V Core Supply Voltage (I)                                                     |

| 26    | LINE_SYNC                             | Line Sync (I/O)                                                                  | Line Sync (I/O)                                                                  |

| 27    | GPIO6/                                | General-Purpose Input/Output 6 (I/O).                                            | General-Purpose Input/Output 6 (I/O).                                            |

|       | BOOT_SOURCE                           | The pull-up/ pull-down value is latched as                                       | The pull-up/ pull-down value is latched as                                       |

|       |                                       | Boot Source input during power up/ reset.<br>Refer section 7.2 for more details. | Boot Source input during power up/ reset.<br>Refer section 7.2 for more details. |

| 28    | SPI DI                                | Non-Volatile Memory SPI interface data                                           | Non-Volatile Memory SPI interface data input                                     |

| 20    | SI I_DI                               | input (I).                                                                       | (I).                                                                             |

| 29    | VSS                                   | Ground (I)                                                                       | Ground (I)                                                                       |

| 30    | VDD IO                                | 3.3V I/O Supply Voltage (I)                                                      | 3.3V I/O Supply Voltage (I)                                                      |

| 31    | SPI CLK                               | Non-Volatile Memory SPI interface clock                                          | Non-Volatile Memory SPI interface clock (O).                                     |

|       |                                       | (O).                                                                             | (0)                                                                              |

| 32    | SPI_CS                                | Non-Volatile Memory SPI interface chips                                          | Non-Volatile Memory SPI interface chips                                          |

|       | _                                     | select (active low) (O).                                                         | select (active low) (O).                                                         |

|       |                                       |                                                                                  |                                                                                  |

| 33    | SPI_DO                                | Non-Volatile Memory SPI interface data                                           | Non-Volatile Memory SPI interface data out                                       |

|       |                                       | out (O).                                                                         | (O).                                                                             |

| 34    | VSS                                   | Ground (I)                                                                       | Ground (I)                                                                       |

| 35    | VDD_C                                 | 1.8V Core Supply Voltage (I)                                                     | 1.8V Core Supply Voltage (I)                                                     |

| 36    | P36                                   | Connect to VDD_IO through a 3.3KΩ resistor (I).                                  | Connect to VDD_IO through a 3.3KΩ resistor (I).                                  |

| 37    | P37                                   | Connect to VSS through a 3.3KΩ resistor (I)                                      | Connect to VSS through a 3.3KΩ resistor (I)                                      |

| 38    | P38                                   | Connect to VDD_IO through a 3.3KΩ resistor                                       | Connect to VDD_IO through a 3.3KΩ resistor (I)                                   |

|       |                                       | (I)                                                                              |                                                                                  |

| 39    | P39                                   | Connect to VDD_IO through a 3.3KΩ resistor                                       | Connect to VDD_IO through a 3.3KΩ resistor (I)                                   |

| 40    | FIGG                                  | (I)                                                                              | C 1 (1)                                                                          |

| 40    | VSS                                   | Ground (I)                                                                       | Ground (I)                                                                       |

| 41 42 | VDD_C<br>P42                          | 1.8V Core Supply Voltage (I)                                                     | 1.8V Core Supply Voltage (I) Connect to VDD_IO through a 3.3KΩ resistor (O)      |

| 42    | F42                                   | Connect to VDD_IO through a 3.3KΩ resistor (O)                                   | Connect to VDD_10 tillough a 3.3K22 lesistol (0)                                 |

| 43    | RESET N                               | Reset Input. Resets all IC logic when low (I).                                   | Reset Input. Resets all IC logic when low (I).                                   |

| 44    | MD IO                                 | MII Management Data Input/Output (I/0)                                           | MII Management Data Input/Output (I/0)                                           |

| 45    | VSS                                   | Ground (I)                                                                       | Ground (I)                                                                       |

| 46    | VDD_IO                                | 3.3V I/O Supply Voltage (I)                                                      | 3.3V I/O Supply Voltage (I)                                                      |

| 47    | MDCLK                                 | MII Management Data Clock (I)                                                    | MII Management Data Clock (O)                                                    |

|       |                                       | The MDCLK signal is a clock reference for the                                    | The MDCLK signal is a clock reference for the                                    |

| 48    | RXD3                                  | MD_IO signal. MII RX Data (O)                                                    | MD_IO signal. MII RX Data (I)                                                    |

| 49    | RXD2                                  | Will KA Bull (0)                                                                 | Will RA Dum (1)                                                                  |

| 52    | RXD1                                  | Data is transferred from the IC across these four                                | Data is transferred from the IC across these four                                |

| 53    | RXD0                                  | lines one nibble at a time                                                       | lines one nibble at a time.                                                      |

| 50    | VSS                                   | Ground (I)                                                                       | Ground (I)                                                                       |

| 51    | VDD_C                                 | 1.8V Core Supply Voltage (I)                                                     | 1.8V Core Supply Voltage (I)                                                     |

| 54    | RX_DV                                 | MII RX Data Valid (O)                                                            | MII RX Data Valid (I)                                                            |

|       | _                                     | TIL C. 1. I. A.                              |                                                                                  |

|       |                                       | This Signal indicates that the data on the RXD [3:0] pins are valid              | This Signal indicates that the data on the RXD [3:0] pins are valid.             |

| 55    | VSS                                   | Ground (I)                                                                       | Ground (I)                                                                       |

| 56    | VDD IO                                | 3.3V I/O Supply Voltage (I)                                                      | 3.3V I/O Supply Voltage (I)                                                      |

| 57    | RX CLK                                | MII RX Clock (O)                                                                 | MII RX Clock (I)                                                                 |

| 31    | I I I I I I I I I I I I I I I I I I I | 1 (-)                                                                            | ( /                                                                              |

Intellon Confidential 13 24002694 Rev. 2

|     |              | PHY Mode (I/O)                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Host/ DTE Mode (I/O)                                                                                                              |

|-----|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| Pin | G: 1         | , ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ` ,                                                                                                                               |

| No. | Signal       | PHY mode is selected by connecting the ASC_DATA/MODE (pin3) to VDD_IO                                                                                                                                                                                                                                                                                                                                                                                                     | Host/DTE mode is selected by connecting the ASC_DATA/MODE (pin3) to VSS                                                           |

| T   |              | through a 3.3KΩ resistor                                                                                                                                                                                                                                                                                                                                                                                                                                                  | through a 3.3KΩ resistor                                                                                                          |

|     |              | The RX Clock is synchronous to the data and is continuous.                                                                                                                                                                                                                                                                                                                                                                                                                | The RX Clock is synchronous to the incoming data and is continuous. This clock operates at 25 MHz (100BaseT) or 2.5MHz (10BaseT). |

| 58  | RX_ER        | MII RX Error (O)                                                                                                                                                                                                                                                                                                                                                                                                                                                          | MII RX Error (I)                                                                                                                  |

|     |              | The RX_ER signal indicates that an error has occurred during frame reception                                                                                                                                                                                                                                                                                                                                                                                              | The RX_ER signal indicates that an error has occurred during frame reception                                                      |

| 59  | TX_EN        | MII TX Enable (I)                                                                                                                                                                                                                                                                                                                                                                                                                                                         | MII TX Enable (O)                                                                                                                 |

|     |              | The MII TX Enable signal indicates that valid data is present on the TXD [3:0] pins.                                                                                                                                                                                                                                                                                                                                                                                      | The MII TX Enable signal indicates that valid data is present on the TXD [3:0] pins.                                              |

| 60  | VSS          | Ground (I)                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Ground (I)                                                                                                                        |

| 61  | VDD_C        | 1.8V Core Supply Voltage (I)                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1.8V Core Supply Voltage (I)                                                                                                      |

| 62  | TXD0         | MII TX data (I)                                                                                                                                                                                                                                                                                                                                                                                                                                                           | MII TX data (O)                                                                                                                   |

| 63  | TXD1         | Data is transferred to the IC across the four lines                                                                                                                                                                                                                                                                                                                                                                                                                       | Data is transferred to the IC across the four lines                                                                               |

| 64  | TXD2<br>TXD3 | one nibble at a time.                                                                                                                                                                                                                                                                                                                                                                                                                                                     | one nibble at a time.                                                                                                             |

| 65  | VSS          | Ground (I)                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Ground (I)                                                                                                                        |

| 66  | VDD IO       | 3.3V I/O Supply Voltage (I)                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3.3V I/O Supply Voltage (I)                                                                                                       |

| 68  | COL          | MH Callinian Datast (O)                                                                                                                                                                                                                                                                                                                                                                                                                                                   | MII Collision Detect (I)                                                                                                          |

| 08  | COL          | MII Collision Detect (O)                                                                                                                                                                                                                                                                                                                                                                                                                                                  | MII Collision Detect (1)                                                                                                          |

|     |              | The MII Collision Detect Signal indicates to                                                                                                                                                                                                                                                                                                                                                                                                                              | The MII Collision Detect Signal indicates to                                                                                      |

|     |              | the MAC that a collision has occurred on                                                                                                                                                                                                                                                                                                                                                                                                                                  | the MAC that a collision has occurred on the                                                                                      |

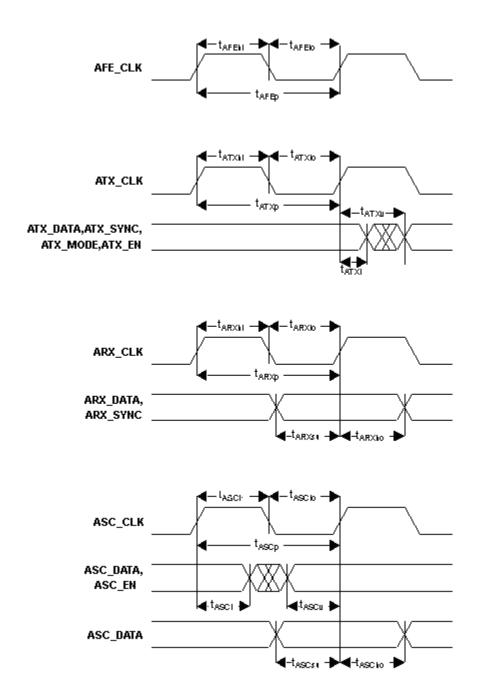

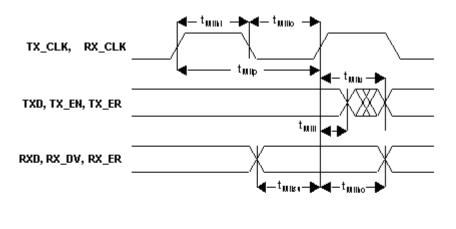

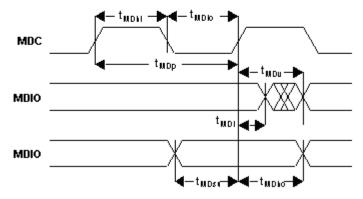

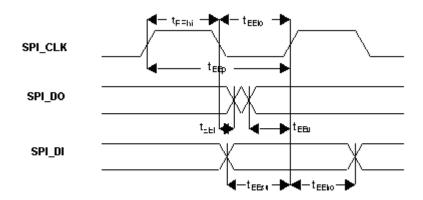

|     |              | the MII interface. MII_COL is an                                                                                                                                                                                                                                                                                                                                                                                                                                          | MII interface and shall remain asserted while                                                                                     |