# A26Y10001-DS-01 DH10P 1.0 BETA Specification Sceet

Design of Systems on Silicon June 10, 2005

|       | REVISION TABLE |      |      |                       |            |                  |  |  |

|-------|----------------|------|------|-----------------------|------------|------------------|--|--|

| VERSI | on Í           | DATE |      | AUTHOR                | REVISED BY | APPROVED BY      |  |  |

| 1.0   | l'une          | 10   | 2005 | José Luis<br>González |            | Francisco Andrés |  |  |

# **Revision History**

|          | 1            |   |  | REVISION HISTORY   |         |  |

|----------|--------------|---|--|--------------------|---------|--|

| REVISION | June 10 2005 |   |  | AUTHOR             | Created |  |

| 1.0      |              |   |  | José Luis González |         |  |

|          |              | e |  |                    |         |  |

# DSS9010/DSS'7700 PLC MODEM

# CH10P 1.0 BETA SPECIFICATION SHEET

## Table of Contents

| 1 | Pi         | RODUCT DESCRIPTION                              | 3             |

|---|------------|-------------------------------------------------|---------------|

|   | 1.1        | Feature Summary                                 |               |

|   | 1.2        | Ordering Information                            | 4             |

|   | 1.3        | General Product Information                     |               |

|   | 1.4        | INCLUDED IN THE RD-DH10P REFERENCE DESIGN       |               |

|   | 1.5        | APPLICATIONS                                    |               |

|   | 1.6        | APPLICATION PROGRAMMING INTERFACE               |               |

|   | 1.7        | Development Environment                         | 6             |

| 2 | IN         | TRODUCTION                                      | 6             |

| 3 | D          | GITAL FRONT END                                 | 6             |

| U |            |                                                 |               |

|   | 3.1        | DSS9010                                         | /<br>7        |

|   | 3.2        | <i>I.1 DSS9010 Interfaces</i><br>MEMORY DEVICES | ······ /<br>Ø |

|   | 3.2<br>3.3 | CLOCK CIRCUITRY AND CRYSTALS                    | o<br>8        |

|   | 3.4        | DH10P External Interfaces                       |               |

|   | 3.5        | POWER SUPPLY CONSUMPTION                        |               |

|   | 3.6        | LEDS AND CONNECTORS                             | 9             |

|   | 3.7        | RESET AND SUPERVISORY CIRCUIT .                 |               |

| 4 | A          | NALOG FRONT END                                 | 11            |

|   | 4.1        | MAIN CHARACTERISTICS                            | 11            |

|   | 4.2        | BLOCK DIAGRAM                                   | 11            |

|   | 4.3        | Description of the $A^{r}$ L                    | 12            |

|   |            | 3.1 Transmission Path                           | 12            |

|   | 4          | 3.2 Reception Party                             | 12            |

|   |            | 3.3 Control.                                    |               |

|   | 4.4        | COUPLINC UNT                                    | 13            |

| 5 | Po         | DWER S 'PI (V                                   | 13            |

|   | 5.1        | SFEC. FICATION                                  | 13            |

| 6 | F          | MC & SAFETY                                     | 13            |

| 7 | F          | VIRONMENTAL PERFORMANCE                         | 1/            |

|   |            | VIRONMENTAL I ERFORMANCE                        | 17            |

| è | Μ          | ECHANICAL SPECIFICATIONS                        | 14            |

|   | 8.1        | PCBs                                            |               |

|   | 8.2        | EXTERNAL VIEW                                   |               |

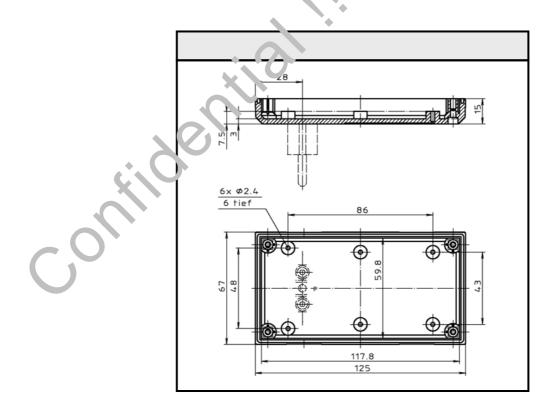

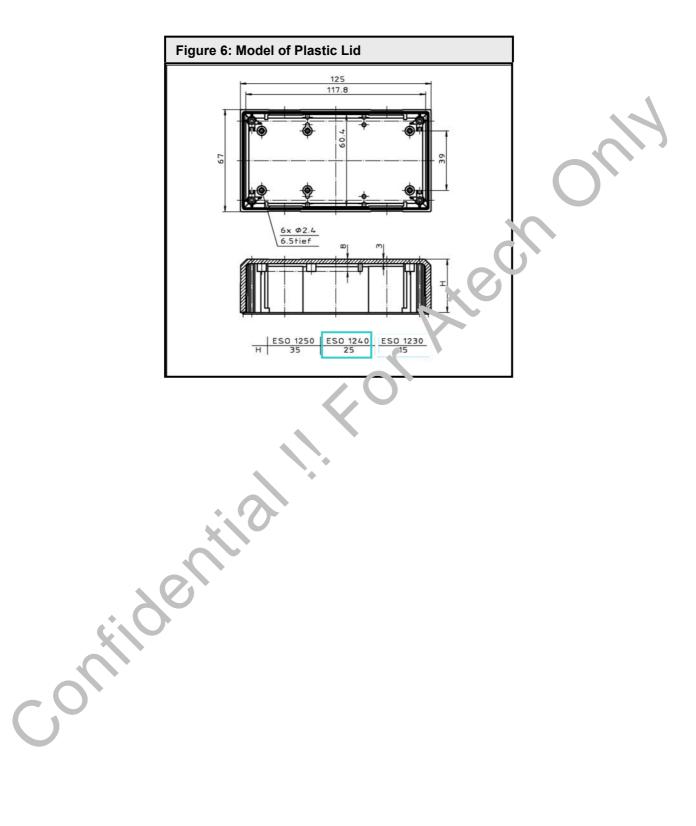

|   | 8.3        | PLASTIC BOX                                     | 15            |

### **1 Product Description**

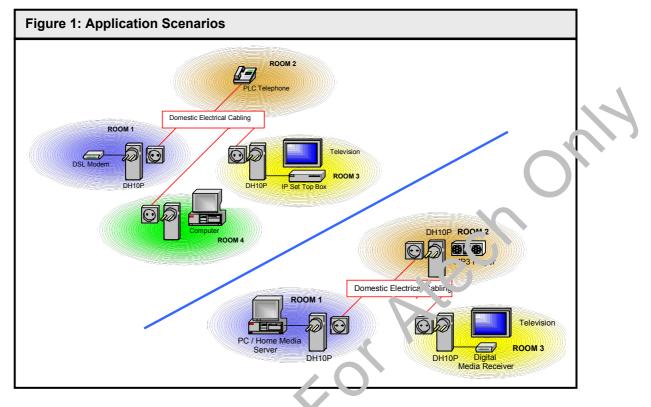

The DH10P reference design is optimized to enable high-speed video and data communications between different devices over the existing domestic power cables. With no configuration, the wall plug provides 100BT Ethernet connectivity and supports transmission speeds in excess of 200 Mbps. The DH10P incorporates DS2 200 Mbps powerline communications technology: the world's highest speed, most fully featured home networking technology, and the only option for transmitting high-quality digital video with full home coverage. Unlike wireless solutions, DS2 PLC networking is not attenuated by walls, and runs on electrical wiring which is present in all tomes

Advanced features such as quality of service management, multicast and network isolation make this the ideal choice for deployment in video on demand or triple play services to connect IP set-top boxes and ADSL residential gatewars. Prug and Play autoconfiguration provides consumers with a trouble-free option to network digital devices anywhere in the home without the need for more cabling, ad gives operators the opportunity provide customers with home-wide services for triple play, video on demand and voice over IP with no need for truck roll.

The DH10P reference design has been developed to minimize cost as well as reduce the format and component count to an absolute minimum. The result is a very low profile design with a minimal bill of materials and advance i manufacturability features such as the Built-In Self Test (BIST). DS2 reference designs provide everything required moving quickly into production of PLC adapters.

#### **1.1 Feature Summary**

#### Highest data rate with bullety and reliability

- Dense OFDM for 20.3 MBps adaptive PLC networking.

- Powerful error corruction system for maximum robustness

- Optimized support for multicast and broadcast traffic

#### Integrated, legislation

- Low-cost 2-chip solution

- . ' nai' 125 mm x 67 mm x 40 mm enclosure

#### Maxi.num security

- Mixed DES/3DES encryption guarantees total data security

- 802.1Q VLAN provide powerful tools for isolating traffic

#### Multiple chip support

- DSS9001 200 Mbps audio/data modem IC with repetition

- DSS9010 200 Mbps data PLC modem IC

#### **Unprecedented flexibility**

- Flexible frequency configuration (from 2 to 34 MHz)

- 10 MHz, 20 MHz, and 30 MHz transmission modes

- Flexible MAC for BPL Access and In-Home AV networking

#### Maximum extensibility

- Flexible API and software development tools

- Remote software upgrade and SNMP support

#### **QoS support**

- Up to 8-level priority queues, with programmable priority classification envine (depending on modem IC)

- Programmable bandwidth and latency allocation for advanced QoS provisioning

#### **Standards compliant**

- Support for access/in-home coexistence

- Programmable notching adapts to evolving EMC rules

#### **1.2 Ordering Information**

To be defined.

#### **1.3 General Product Information**

#### 1.4 Included in the RD-DH10P Reference Design

- Gerber Layout Files

- Help Desk Support

- Schematic Files

- Bills of Materials

- Pick and Place File

#### 1.5 Applications

- **Tripler 'ay over DSL** extension- Connect set-top boxes to the DSL modem with non-ded for cabling

- Scond Receiver for CATV/Satellite Watch two different channels in Cifferent rooms

- Networked PVR Players Watch multimedia anywhere in the home

- PC Networking Instantly convert a PC into a home media server

- **SOHO Routers** Better coverage than wireless

- HDTV Televisions Receive content from a remote media server

- WiFi Extenders Overcome the range limitation of wireless

#### **1.6 Application Programming Interface**

To facilitate the development of custom applications for the microprocessor embedded in the DS2 digital modem IC, DS2 provides a powerful API. This gives developers the ability to extend and adapt the powerful high-level features provided, such as addition

of applications using the TCP/IP stack, customization of the QoS and networking capabilities.

#### **1.7 Development Environment**

DS2 has created a sophisticated software development environment allowing custom applications to be developed, verified, and added to the extensive features offered by the DS2 digital modem IC device. The development environment is based on industry standard tools for fast and efficient application development.

#### 2 Introduction

The DH10P is a DSS9010-based in-home modem. Its main objective is to extend access to all sockets in the home, covering some of the in-home PLC data market.

The DH10P in-home modem provides a link between the povertice betwork and a Fast Ethernet 10/100M port.

# **3** Digital Front End

The model of the source of the second second

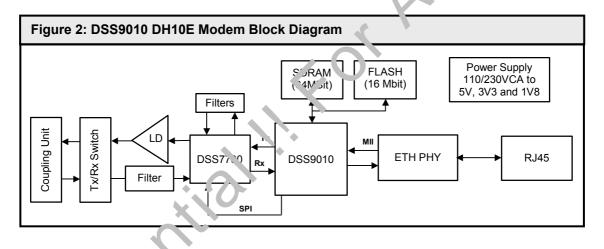

#### DSS9010

- Memory devices (16 megabits of FLASH and 64 megabits of SDRAM)

- Clock circuitry and crystals

- Realtek's RTL8201CL Single Port 10/100M Fast Ethernet Phyceiver

- LEDs and connectors

- Reset and supervisory circuit

#### 3.1 DSS9010

The DSS9010 stands at the core of the in-home modem, at location UD1. It is in charge of controlling all data traffic on the board. It can deliver data rates in excess of 200 Mbps through the powerline port. It is specially designed to operate as a Customer Premises Equipment (CPE) modem or as a home networking device. The DSS9010 forwarding table has room for 16 MAC addresses, making it ideal for developing very low-cost products for the in-home market. The DSS9010 features an industrial standard Media Independent Interface (MII).

#### 3.1.1 DSS9010 Interfaces

#### 3.1.1.1 SPI Interface

An industry standard SPI bus is used by the DSS9010 to interface with several SPI compatible devices. Via the SPI bus, the DSS9010 interfaces with menory levices, analog IC's, etc. The DSS9010 SPI interface supports all four operational modes described in the SPI specification. SPI clock frequencies for each individual SL compatible device might differ. For this reason, the SPI\_CLOCK signal might not ne test will be continuous.

| Table 1: SPI Interface Signals |        |   |                                                                                                                 |  |  |  |

|--------------------------------|--------|---|-----------------------------------------------------------------------------------------------------------------|--|--|--|

| SIGNAL NAME                    | TYPE   | # | DESCRIPTION                                                                                                     |  |  |  |

| SPI_CLOCK                      | Output | 1 | SPI clock. All control and data signals are synchronous to this signal. Frequency is programmable up to 40 MHz. |  |  |  |

| SPI_OUT                        | Output | 1 | SP' serual data out.                                                                                            |  |  |  |

| SPI_IN                         | Input  | 1 | SPI serial data in.                                                                                             |  |  |  |

| SPI_NCS(3:0)                   | Output | 4 | Chip select signals for SPI devices.                                                                            |  |  |  |

*Note: SPI\_NCS(3) is used to s lest the DSS7700 analog chip.*

#### 3.1.1.2 UART Interface

The DSS9010's *DF.*R1 block is a limited implementation of the 8250 device. The DSS9010 only prevides the Tx and Rx lines of the RS-232 standard. A XON-XOFF protocol is readed to communicate between the DSS9010 and a third device. The maximum bend speed of the UART is 9600 bauds.

| Table ?: UART Interface Signals |                                 |   |                       |  |  |  |  |  |

|---------------------------------|---------------------------------|---|-----------------------|--|--|--|--|--|

| SIG IAL NAME                    | SIG IAL NAME TYPE # DESCRIPTION |   |                       |  |  |  |  |  |

| TXD_UART                        | Output                          | 1 | Serial port data out. |  |  |  |  |  |

| RXD_UART                        | Input                           | 1 | Serial port data in.  |  |  |  |  |  |

#### 3.1.1.3 GPIO Interface

The DSS9010 provides nine general-purpose input/output pads. Each of these pads can be configured as input or output. Every input can be used as an IRQ source for the

internal microprocessor. These lines are provided to support customer applications running on the DSS9010.

Besides the functionality assigned to the GPIO signals, these pins also provide access to a CPU JTAG debug port. These signals are multiplexed in such a manner that:

| GPIO     | FUNCTION                 | JTAG |

|----------|--------------------------|------|

| GPIO (0) | -                        | TCK  |

| GPIO (1) | -                        | TMS  |

| GPIO (2) | PLC L/A LED              | BUSY |

| GPIO (3) | -                        | TDI  |

| GPIO (4) | -                        | TDO  |

| GPIO (5) | HW RESET (NOT YET IN FW) |      |

| GPIO (6) | -                        |      |

| GPIO (7) | -                        |      |

| GPIO (8) | ETH L/A LED              | -    |

#### 3.2 Memory Devices

There are several memory devices in the DS \$4010 DH10P modem. A FLASH memory is used to store boot and firmware co.'e. SS1's SST39VF1681 in a TSOP-48 package provides 16 megabits of non-volatile memory, located at UD4.

Besides the FLASH memory, 64 megabits of SDRAM are used as system memory. This SDRAM device operate at clock rates of 160 MHz. The SDRAM used for system memory is Samsung's K4SC41<sup>(2)</sup>2H-TC60 in a TSOP-54 package at location UD3.

#### 3.3 Clock Circuitry and Crystals

CMAC's 80M H<sub>2</sub> C<sup>1</sup> PS-73I-A oscillator of 80MHz and  $\pm$ 25ppm is used at location UD8 as the rain system clock, and also as the clock for the internal AD/DA converters inside the DS55010.

Real. k's RTL8201CL needs a 25 MHz clock signal, which is generated using a 25 MHz crystal at location XD2.

#### .4 DH10P External Interfaces

The DSS9010 DH10P modem offers two external interfaces. These interfaces are:

• *Powerline*: This port connects directly to the AC mains. A line coupler protects the modem from the high voltage of the mains and allows through the high frequency data signals. The transmission path converts the data to analog levels, as well as performs the filtering and amplification of the signal before

sending it to the powerline. The reception path amplifies and filters the signal before the analog to digital conversion and the digital demodulation blocks.

• *10/100BaseTx*: The modem offers one Fast Ethernet 10/100 Mbps full duplex interface (half duplex mode not supported) at connector JD2 (RJ45 connector). This interface is implemented with Realtek's RTL8201CL physical layer device at location UD2.

The RTL8201CL is a single-port phyceiver with an MII/SNI (Serial Network Interface). It integrates 10Base-T and 100Base-TX functions and some e. tra power management features into a 48-pin single chip, which is used in 10,100 Fast Ethernet applications.

#### **3.5 Power Supply Consumption**

There are three main voltages that are used in the DSS9010 DH10<sup>P</sup> n.odem: 5 V, 3.3 V and 1.85 V. The 3.3 and 1.85 voltages are filtered to feed the an 1.3g front end (3V3\_A, 1V8\_A). The estimated typical power consumption is shown in Table 4.

| Table 4: Typical Power Consumption |                     |                      |                       |              |  |  |  |  |

|------------------------------------|---------------------|----------------------|-----------------------|--------------|--|--|--|--|

| OUTPUT                             | DFE CURRENT<br>(mA) | AFE CURRFNT<br>(r:A) | TOTAL CURRENT<br>(mA) | POWER<br>(W) |  |  |  |  |

| 5V                                 | -                   | <u>5</u> 07 =        | 200                   | 1            |  |  |  |  |

| 3V3                                | 170                 | 161                  | 350                   | 1.16         |  |  |  |  |

| 1V85                               | 900                 | 4                    | 904                   | 1.67         |  |  |  |  |

| Total Power (W)                    | -                   | -                    | -                     | 3.82         |  |  |  |  |

#### 3.6 LEDs and Connectors

Three LEDs have been a ded to the modem to indicate functional status, as well as correct power supply operations. These LEDs are described in the same order as they appear on the from  $t_{\rm p}$  and of the modem:

| Table 5: LED Signals |  |                                |                          |  |  |  |  |

|----------------------|--|--------------------------------|--------------------------|--|--|--|--|

| LED                  |  | ON/FLASHING                    | OPERATION                |  |  |  |  |

| DE                   |  | PLC link and activity detected | Active low with GPIO (2) |  |  |  |  |

| D⊾3                  |  | ETH link and activity detected | Active low with GPIO (8) |  |  |  |  |

| 275                  |  | PLC power on                   | 3V3 presence             |  |  |  |  |

There are three connectors on the board:

• *External Signal/Power:* Since the DH10P modem has an internal coupling unit and power supply, the modem has an internal power socket connected to signals PLC1 and PLC2. The modem should be connected directly to the AC mains.

- *Ethernet:* The DH10P modem connects to a customer's host PC through an Ethernet port. A pulse jack RJ45 connector with internal magnetics and two LEDs is located at JD2. The two LEDs, green and yellow, are active and blink depending on the status:

- *Green LED:* Active when the port is linked.

- *Yellow LED:* Active when the port is linked in 100Base-TX and blinking when transmitting or receiving data.

- *JTAG*: This connector for debugging purposes can be mounted on the bottom side of the board and has the necessary signals for serial communication with the DSS9010 using an external JTAG box. It is stuffed on JD10. Pin: 4 and 10 are the SERIAL\_RX and SERIAL\_TX of the serial interface. It is necessary to add an external transceiver (e.g. MAX232 included in the JTAG box) to adjust the levels of these signals. Table 6 shows the assignment of each pin.

| Table 6: JTAG Connector |            |        |                                          |  |  |  |

|-------------------------|------------|--------|------------------------------------------|--|--|--|

| PIN                     | NAME       | TYPE   | INCTION                                  |  |  |  |

| 1                       | +5V        | Power  | 5 Volts                                  |  |  |  |

| 2                       | CTRL_FLASH | Input  | Remote three , tate control of the FLASH |  |  |  |

| 3                       | RESET      | Input  | Externa reset                            |  |  |  |

| 4                       | SERIAL_RXD | Input  | Serial recoption                         |  |  |  |

| 5                       | TDI        | Input  | JT, G d ata input                        |  |  |  |

| 6                       | TMS        | Input  | JTAG control output                      |  |  |  |

| 7                       | BUSY       | Cutput | TAG control input                        |  |  |  |

| 8                       | ТСК        | Input  | JTAG clock input                         |  |  |  |

| 9                       | GROUND     | Power  | Ground                                   |  |  |  |

| 10                      | SERIAL_TXD | Output | Serial transmission                      |  |  |  |

| 11                      | TDO        | Output | JTAG data output                         |  |  |  |

| 12                      | GROUI 'D   | Power  | Ground                                   |  |  |  |

|                         |            |        |                                          |  |  |  |

The user should be careful not to insert a connector upside down, since this r. v. arse permanent damage to the user's equipment, as well as the direct conjection with a PC serial port without the use of an external transceiver.

## 3.7 Reset and Supervisory Circuit

There is a single power supply supervisory circuit on the board at location UD9 composed of Maxim's MAX6384XS29D3-T, which supervises 3V3. Whenever 3V3 falls below the factory-set reset thresholds (2.93 V in this case), the reset output asserts and remains asserted for a minimum reset timeout period after 3V3 rises above the reset threshold (140 ms for D3 option) –  $\pm 2.5\%$  reset threshold accuracy over temperature (-40°C to +125°C).

### 4 Analog Front End

#### 4.1 Main Characteristics

- Analog Front End (AFE) based on DS2's DSS7700 PLC analog chip

- Maximum PSD transmitted (30 MHz signal bandwidth): -58 dBm/Hz

- Programmable transmission gain: 25 dB & 13 dB

- Programmable reception gain: 30dB down to -12dB, in 6dB steps

- Maximum signal frequency: 30 MHz

- Coupling unit integrated on the board

- Power supply integrated on the board

- Analog-to-Digital Converter integrated in the DSS9010

- Digital-to-Analog Converter integrated in the DSS9010

#### 4.2 Block Diagram

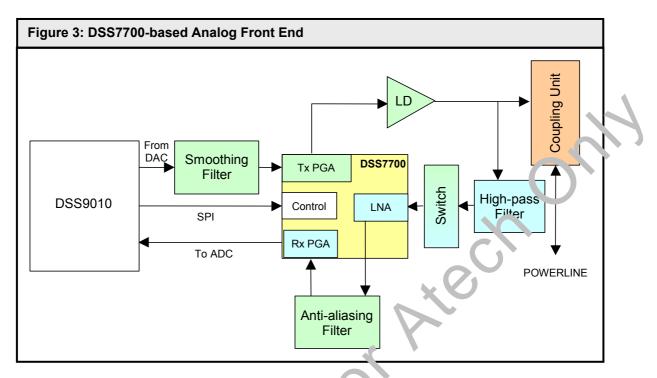

The AFE is based on the DSS7700 chip. It also includes the line driver, passive filters and the Rx switch.

The DSS7700 incorporates several amplifiers. In transmission, there is a Programmable Gain Amplifier (PGA) before the line driver whose gains can be changed to inject different power levels on the line. In reception there are two amplifiers, the Low Noise Amplifier (LNA) and the PGA for conducting the received signal to the ADC (Analog-to-Digital Converter) dynamic range.

The PGAs are controlled from the DSS9010 AGC logic algorithm, through the SPI port.

The passive filters are RLC filters designed for shaping the signal in transmission and for rejecting interference frequency bands in reception.

The Rx switch has been designed with bipolar transistors in series with the signal path.

Several debu; te. t and validation features have been implemented in the PCB.

The block diagram is shown in figure 3.

The SPI signals from the DSS9010 and the AFF's control signals (reception and transmission gains, etc.) are generated by u.e. firmware and they are the same signals as those found in the DU100.

#### **4.3 Description of the AFE**

#### 4.3.1 Transmission Path

The output signal from the Digital-to-Analog Converter (DAC) is filtered by the smoothing filter, and then amplified by the transmission Programmable Gain Amplifier (Tx PGA) from the DSS7700, then continues to the line driver. The signal is then applied to the powerline through the coupling unit.

#### 4.3.2 K. ception Path

The reception signal is filtered by the external high-pass filter, enters the reception switch and i, is amplified by the Low Noise Amplifier (LNA) from the DSS7700. After that it is filtered by the antialiasing filter and goes to the reception Programmable Gain Amplifier (Rx PGA) from the DSS7700. Then, it passes to the Analog-to-Digital Converter (ADC).

#### 4.3.3 Control

The control of the gains of the different DSS7700 amplifiers and the selection of the Tx and Rx modes are implemented inside the chip, which is controlled by the digital chip via the SPI.

#### 4.4 Coupling Unit

A X1/Y1 capacitor and a signal transformer are used as the coupling unit to the powerline. They also isolate the modem from the powerline voltage.

#### 5 Power Supply

#### 5.1 Specification

The power supply specification is shown in Table 7:

| Table 7: Power Supply Specification |                       |      |       |       |           |                                     |  |

|-------------------------------------|-----------------------|------|-------|-------|-----------|-------------------------------------|--|

| DESCRIPTION                         | SYMBOL                | MIN  | TYP   | MAX   | UNITS     | CO. IMENTS                          |  |

| INPUT                               |                       |      |       |       |           |                                     |  |

| Voltage (Nominal)                   | V <sub>IN</sub>       | 100  |       | 240   | VAC       |                                     |  |

| Frequency (Nominal)                 | F <sub>LINE</sub>     | 50   |       | 60    | <u>}.</u> |                                     |  |

| OUTPUTS                             |                       |      |       |       |           |                                     |  |

| Output Voltage 1                    | V <sub>OUT1</sub>     | 3    | 3.3   | 3.6   | V         | Est DOD                             |  |

| Output Ripple Voltage 1             | $V_{RIPPLE1}$         |      | •     | 200   | $mV_{PP}$ | For PSD<br>(See Note <sup>1</sup> ) |  |

| Output Current 1                    | I <sub>OUT1</sub>     | 0.10 | 0.? o | J.60  | Α         |                                     |  |

| Output Voltage 2                    | V <sub>OUT2</sub>     | 1.75 | 1.85  | 1.95  | V         | For PSD                             |  |

| Output Ripple Voltage 2             | $V_{RIPPLE2}$         |      |       | 120   | $mV_{PP}$ | (See Note <sup>1</sup> )            |  |

| Output Current 2                    | I <sub>OUT2</sub>     | 0.70 | 0.90  | 1.10  | Α         | (00011010)                          |  |

| Output Voltage 3                    | V <sub>OUT3</sub>     | - 75 | 5.00  | 5.25  | V         |                                     |  |

| Output Ripple Voltage 3             | V <sub>RIPPLE</sub> ن | •    |       | 175   | $mV_{PP}$ | For PSD<br>(See Note <sup>1</sup> ) |  |

| Output Current 3                    | I <sub>0' /13</sub>   | 0.15 | 0.2   | 0.22  | Α         | (00011010)                          |  |

| TOTAL OUTPUT POWER                  |                       |      |       |       |           |                                     |  |

| Typical Output Power                | POUT                  |      | 3.82  |       | W         |                                     |  |

| Maximum Output Powe.                | POUT-MAX              |      |       | 5.115 | W         |                                     |  |

| Efficiency                          | η                     | 65   |       |       | %         | @Full Load 70 <sup>O</sup> C        |  |

**NOTE**<sup>1</sup>: Differential input noise at mains (PSD) -144 dBm/Hz to -150 dBm/Hz from 4 MHz to  $34 \text{ Ma}^{17}$ .

# 6 FMC & Safety

DS2 is working to meet with the essential requirements stated in the EMC 89/336/EEC) and Low Voltage (73/23/EEC) European Directives in its DH10P design.

To comply with the requirements of the EMC Directive, DS2 is working to fit its design to pass the corresponding tests stated in the EN 55022 (Emissions), EN 55024 (Immunity), EN 61000-3-2 (Harmonics) and EN 61000-3-3 (Flicker).

To comply with the requirements of the Low Voltage Directive, DS2 is working to fit its design to pass the corresponding tests stated in the EN 60950-1:2001 (IEC 60950-1:2001) standard.

Fulfilling with the above-mentioned standards, the DH10P design will be able to meet with the EMC and Safety requirements for EU CE marking.

#### 7 Environmental Performance

The specifications for DH10P wall plug format are the following:

- Thermal range of 0-40°C

- Up to 6.6W dissipated in a plastic box

- IP20 protection

#### 8 Mechanical Specifications

#### 8.1 PCBs

The DH10P modem uses two Printed Circuit Assemb'ies (SB10P and PS10P).

The SB10P board is a 6-layers printed circun board. Its dimensions are 88 mm x 55 mm  $(3.464" \times 2.165")$ , and has been manufactured using FR-4 dielectrics. Its thickness between dielectrics is 1.354 mm (53.51 mi).

Its stack-up is the following:

- Layer 1: External Signal layer

- Layer 2: Grou 10 Plane

- Layer 3: Power Plane and Internal Signal layer

- Layer 1: 1 ° wer Plane

- Layer 5: Ground Plane

- Ayer 6. External Signal layer

Both external layers are used to mount components.

The 1510P board is a 2-layers printed circuit board. Its dimensions are 88 mm x 55 mm (3.464" x 2.165"), and has been manufactured using one FR-4 dielectric. Its thickness between dielectrics is 1.6 mm (63 mils).

Only the top layer is used to mount components.

#### 8.2 External View

The three status LEDs (previously described) are located on the front panel of the modem and on the bottom side of the enclosure there is a RJ45 Fast 10/100M Ethernet port.

#### 8.3 Plastic Box

The following figures illustrate different points of view of the modem's plastic box.